Product Details

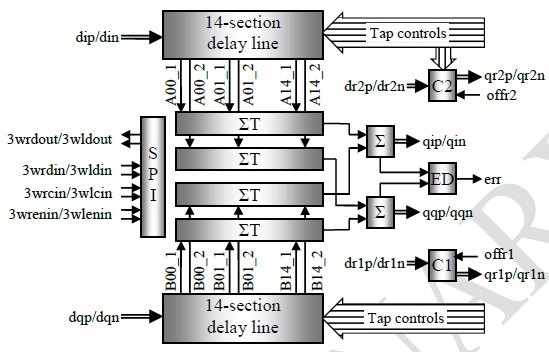

Fig. 1 Functional Block Diagram

The ASNT6171-KMO part is a dual 15-tap FIR filter for processing of two analog signals dip/din and dqp/dqn. It includes two passive delay lines with 14 matching sections and three loss-compensating buffers in each one. The buffers feature gain and frequency response adjustment. The signals from all 15 nodes of both delay lines are delivered to 4 summation blocks (ΣT) through taps. Each tap in both delay lines includes two buffers with individually controlled weight and sign.

The part also includes two output summation blocks (Σ) that allow for mixing of equalized signals from both channels. The resulting signals are delivered to two output analog ports qip/qin and qqp/qqn. The output buffers may have a separate supply voltage for adjustment of the output common-mode voltage level. They also have additional adjustments of gain and frequency response.

The equalized signals are also processed by an error detector block (ED) to produce an error signal that indicates the signal deviation from an ideal pulse shape.

The part includes two calibration blocks for initial calibration of gain and frequency response in the output buffers (C1) and in taps (C2). All analog input/output ports have internal 50Ohm terminations to positive supply rails. The output ports require external 50Ohm DC terminations to the same supply rails or AC terminations to ground.

All functions are controlled through a dual 3-wire SPI interface that has two 4-pin ports. Both ports support standard 3-wire slave functionality. The chip includes two temperature sensors implemented as large diodes with their cathodes connected to vee and their anodes connected to tsens1 and tsens2 ports. The sensors represent temperatures at the top and the bottom of the die respectively.