Product Details

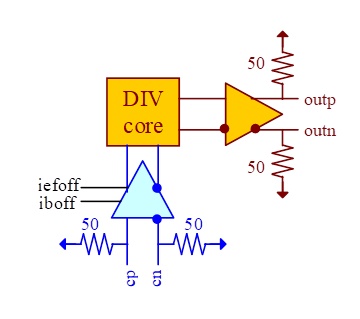

Fig.1 Functional Block Diagram

The ASNT8730-KHC provides broadband clock divide-by-2 functionality, and is intended for use in high-speed measurement / test equipment. The IC can process a high-speed clock input signal cp/cn and deliver a high-speed clock output signal qp/qn with 50% duty cycle. Static control signals iboff and iefoff provide option to increase device bandwidth by slightly increasing power consumption. In default (unconnected) state control signals are pulled-up to vcc to save power consumption. To activate boost mode low level voltage should be provided to both or just one of control inputs.

The part’s I/O’s support the CML logic interface with on chip 50 Ohms termination to vcc and may be used differentially, AC/DC coupled, single-ended, or in any combination. In the AC-coupling mode, the input termination provides the required common mode voltage automatically. The differential DC signaling mode is recommended for optimal performance.