# ASNT6172A-KMO Asynchronous FIR Filter and 2x2 Analog Switch

- Dual FIR filter with 9 fully controlled taps for each input analog signal

- Fully differential CML-type analog input interfaces

- Two independent fully differential CML-type analog outputs

- Operates as an analog non-blocking 2x2 switch with a possibility to mix weighted input signals

- High bandwidth DC-28Gbps / 20GHz

- Total gain up to 6dB

- Dual-port 3-wire SPI for tap weight and sign adjustment

- Additional frequency response and gain adjustment through the SPI

- Independent power supplies for analog and digital sections

- Power consumption: <1.25*W*

- Fabricated in SiGe for high performance, yield, and reliability

- Custom CQFP 64-pin package

## **DESCRIPTION**

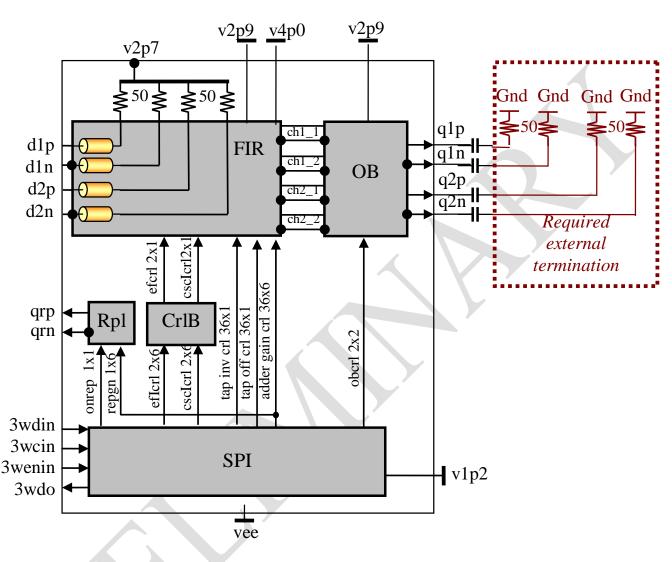

Fig. 1. Functional Block Diagram

The IC shown in Fig. 1 is a two-channel differential analog 9-tap FIR filter. It receives two high-speed analog signals through its differential input ports d1p/d1n and d2p/d2n. Each channel of FIR has 9 dual taps. Each tap provides two copies of its input signal with controlled polarities. The signals are then processed by analog adders with controlled weight coefficients to perform the pre-emphasis operation. The resulting 4 analog signals (the first and the second signals from the first and the second channels) are sent to the output buffer block that converts them into two output analog signals delivered to linear differential ports out1p/out1n and out2p/out2n. The first output port presents either individual first signal from any channel, or a sum of both first signals. It can be also completely disabled. The second output port presents the second signals from both channels with the same operational modes. Both ports operate in CML-type mode and require external 50*Ohm* terminations.

All chip functions are controlled by internal digital signals delivered through a 3-wire serial-to-parallel interface (SPI) that operates in combination with an internal control block CrlB.

The chip includes a 1-tap replica Rpl that can be independently enabled and used for initial gain calibration as described below.

#### FIR

The FIR consists of two identical channels. At the input of each channel there is a differential transmission line that includes 10 identical sections connected in series to provide ten equal delays. The connection nodes of the sections serve as inputs for 9 taps. The ends of the last section have internal 50*Ohm* terminations to a separate internally generated power supply v2p7. The last section is required for achievement of matching conditions for all taps.

Each tap includes a pair of dual buffers (buf1 and buf2) which allows for generation of two copies of the tap's input signal with polarities individually selected by 1-bit binary signals chX\_inv1 and chX\_inv2, where "0" corresponds to a direct output signal and "1" corresponds to an inverted output signal. Dual buffers in each tap can be individually disabled by special 1-bit binary signals chX\_off1="0" or chX\_off2="0". The buffers of different taps have slightly different gains and internal peaking in order to compensate for transmission line losses.

The 9 pairs of delayed copies of the differential input signal with set polarities are then processed by two 2-stage adders in order to create two linear sums of weighted tap signals. The first stage of each adder consists of three 3-to-1 adders and combines 9 input signals into 3 intermediate signals. The second stage combines those intermediate signals into 1 output signal. Identical 3-to-1 analog adders with digital controls of each input's weight are used in both stages. The control circuitry of the 3-to-1 adder is designed in such a way that the combined weight of all 3 inputs does not exceed the maximum weight of one tap. The control circuitry receives three 6-bit binary signals: the first weight chX\_gncYZ1, the second weight chX\_gncYZ2, and the maximum possible weight chX\_gnmxY, and converts them into another three 6-bit binary signals that control the actual weights of all three inputs. Here X is the channel number 1 or 2; Z is the 2-stage adder number 1 or 2; and Y is the 3-to-1 adder number 1, 2, 3, or 0, where the adders 1, 2, and 3 represent the first stage and the adder 0 represents the second stage. The corresponding algorithm is detailed in Table 1.

| Input number   Control signal |            | Formula       | Condition                          |

|-------------------------------|------------|---------------|------------------------------------|

| 1 chX_crlYZ1                  |            | chX_gncYZ1    | if chX_gncYZ1≤ chX_gnmxY           |

|                               |            | chX_gnmxY     | if chX_gncYZ1> chX_gnmxY           |

| 2 chX_crlYZ2                  |            | chX_gncYZ2    | if R1=(chX_gnmxY-chX_gncYZ1)>0 and |

|                               |            |               | ichX_gncYZ2≤ R1                    |

|                               |            | R1            | if R1>0 and chX_gncYZ2>R1          |

|                               |            | 0             | if R1 ≤0                           |

| 3                             | chX_crlYZ3 | R1-chX_gncYZ2 | if R1>0 and R2=R1-chX_gncYZ2>0     |

|                               |            | 0             | if R1≤0 or R2≤0                    |

Table 1. Wight Control Algorithm

The maximum weight can be adjusted depending on the fabrication process corner. The required value of the maximum weight is defined during initial calibration. The calibration is performed using a replica block Rpl that is described below.

Rev. 0.2.2 3 December 2020

Each tap can be enabled/disabled and its weight and polarity are defined by internal binary signals set through SPI that is also described below.

#### OB

The output buffer (OB) takes two pairs of analog signals from the two FIR channels (ch1\_out1, ch1\_out2, ch2\_out1, and ch2\_out2) and delivers them to the two output ports q1p/q1n and q2p/q2n as defined by 2-bit binary control signals obcrl1<1:0> and obcrl2<1:0> according to Table 2. Here X is the channel number 1 or 2.

obcrlX<1>

obcrlX<0>

qX

0

0

Output disabled

0

1

ch1\_outX

1

0

ch2\_outX

1

1

0.5\*(ch1\_outX)+0.5\*(ch2\_outX)

Table 2. Output Buffer Operational Modes

#### CrIB

The control block (CrlB) converts binary signals from SPI into analog voltages that control internal peaking and linearity parameters of FIR channels. The peaking can be adjusted by 6-bit binary signals chX\_ief<5:0> where higher values corresponding to higher bandwidth with associated high-frequency peaking of the channel's frequency response. The linearity can be adjusted by 6-bit binary signals chX\_icsc<5:0> where higher values correspond to higher linearity at low weights.

#### **Rpl**

The tap replica (Rpl) is used for initial tap gain calibration to ensure the optimal maximum data signal swing at the outputs of the first stages of both adders.

Rpl is an exact copy of Tap1. In the optimal state, it should generate a predefined DC voltage difference between its outputs qrp and qrn. This difference should be adjusted to the value specified in ELECTRICAL CHARACTERISTICS using the 6-bit binary signal ch1\_gnmx1. Rpl is used for initial calibration only and can be completely disabled by the binary signal onrep="0".

#### SPI

The 3-wire SPI operates in slave mode and accepts three CMOS signals: 3wenin (SSn), 3wcin (SCLK), and 3wdin (MOSI) as described in ELECTRICAL CHARACTERISTICS. Additional CMOS data output 3wdout (MISO) is provided for control purposes.

SPI converts 40 input serial bytes into 115 parallel binary control signals. The SPI byte description is presented in Table 3.

Office: (310) 530-9400 Fax: (310) 530-9402

www.adsantec.com

Table 3. SPI Control Bytes

| SPI     | Byte     | Bit Number       |                                     |  |   |   |          |          |             |                            |

|---------|----------|------------------|-------------------------------------|--|---|---|----------|----------|-------------|----------------------------|

| Section | Number   | 7 (MSB for Left) | 6                                   |  |   | 3 | 2        | 1        |             | 0 (MSB for Right)          |

| Left    | 1        | onrep            | X                                   |  |   |   |          | ch1      | _gnmx       |                            |

|         | 2        | obcrl1           |                                     |  |   |   |          | ch1      | _gnmx       | .0                         |

|         | 3        | ch1_off1(1)      | ch1_inv1(1)                         |  |   |   |          | ch1      | _gnc11      | 1                          |

|         | 4        | ch1_off1(2)      | ch1_inv1(2)                         |  |   |   |          | ch1      | _gnc1       | 12                         |

|         | 5        | ch1_off1(3)      | ch1_inv1(3)                         |  |   |   |          | ch1      | _gnc12      | 21                         |

|         | 6        | ch1_off1(4)      | ch1_inv1(4)                         |  |   |   |          | ch1      | _ gnc12     | 22                         |

|         | 7        | ch1_off1(5)      | ch1_ inv1(5)                        |  |   |   |          | ch1      | _gnc21      | 1                          |

|         | 8        | ch1_off1(6)      | ch1_inv1(6)                         |  |   |   |          |          | gnc2        |                            |

|         | 9        | ch1_off1(7)      | ch1_inv1(7)                         |  |   |   |          |          | _gnc22      |                            |

|         | 10       | ch1_off1(8)      | ch1_inv1(8)                         |  |   |   |          |          | _gnc22      |                            |

|         | 11       | ch1_off1(9)      | ch1_inv1(9)                         |  |   |   |          |          | _gnc31      |                            |

|         | 12       | ch1_off2(1)      | ch1_inv2(1)                         |  |   |   |          |          | _gnc3       |                            |

|         | 13       | ch1_off2(2)      | ch1_ inv2(2)                        |  |   |   |          |          | _gnc32      |                            |

|         | 14       | ch1_off2(3)      | ch1_inv2(3)                         |  |   |   |          |          | _ gnc32     |                            |

|         | 15       | ch1_off2(4)      | ch1_ inv2(4)                        |  |   |   |          |          | _gnc01      |                            |

|         | 16       | ch1_off2(5)      | ch1_ inv2(5)                        |  |   |   |          |          | gnc0        |                            |

|         | 17       | ch1_off2(6)      | ch1_ inv2(6)                        |  |   |   |          |          | _gnc02      |                            |

|         | 18       | ch1_off2(7)      | ch1_ inv2(7)<br>ch1_ inv2(8)        |  |   |   |          |          | _ gnc02     |                            |

|         | 19       | ch1_off2(8)      | ch1_ef1 (DAC)                       |  |   |   |          |          |             |                            |

|         | 20       | ch1_off2(9)      | ch1_csc (DAC)                       |  |   |   |          |          |             |                            |

| D' 1    | 21       | X                | X                                   |  |   |   |          |          | ef2 (DA     |                            |

| Right   | 22       |                  | C) (reversed bit                    |  |   |   |          | X        | 2(0)        | X                          |

|         | 23       |                  | C) (reversed bit                    |  |   |   |          | ch2_ inv |             | ch2_off2(9)                |

|         | 24       |                  | C) (reversed bit                    |  |   |   |          | ch2_inv  |             | ch2_off2(8)                |

|         | 25       |                  | 2 (reversed bit o                   |  |   |   |          | ch2_ inv |             | ch2_off2(7)                |

|         | 26<br>27 |                  | (reversed bit of 2 (reversed bit of |  |   |   |          | ch2_inv  |             | ch2_off2(6)                |

|         | 28       |                  | (reversed bit of                    |  |   |   |          | ch2_ inv |             | ch2_off2(5)<br>ch2_off2(4) |

|         | 29       |                  | 2 (reversed bit of                  |  |   |   |          | ch2_ inv |             | ch2_off2(3)                |

|         | 30       |                  | (reversed bit of                    |  |   |   |          | ch2_ inv |             | ch2_off2(2)                |

|         | 31       | ch2_gnc32        |                                     |  |   |   | ch2_ inv |          | ch2_off2(1) |                            |

|         | 32       |                  | (reversed bit of                    |  |   |   |          | ch2_ inv |             | ch2_off1(9)                |

|         | 33       |                  | 2 (reversed bit of                  |  |   |   |          | ch2_ inv |             | ch2_off1(8)                |

|         | 34       | ch2_gnc221       |                                     |  |   |   | ch2_ inv |          | ch2_off1(7) |                            |

|         | 35       | ch2_gnc21        |                                     |  |   |   | ch2_ inv | ` '      | ch2_off1(6) |                            |

|         | 36       |                  | (reversed bit of                    |  |   |   |          | ch2_ inv |             | ch2_off1(5)                |

| 4 7     | 37       |                  | 2 (reversed bit of                  |  |   |   |          | ch2_ inv |             | ch2_off1(4)                |

|         | 38       |                  | (reversed bit o                     |  |   |   |          | ch2_ inv |             | ch2_off1(3)                |

|         | 39       |                  | 2 (reversed bit of                  |  | , |   |          | ch2_ inv |             | ch2_off1(2)                |

|         | 40       |                  | (reversed bit o                     |  | _ |   |          | ch2_inv  |             | ch2_off1(1)                |

| /       | 41       | <u> </u>         | (reversed bit o                     |  |   |   |          | _        |             | versed bit order)          |

|         | 42       | )                | (reversed bit o                     |  |   |   |          | X        |             | X                          |

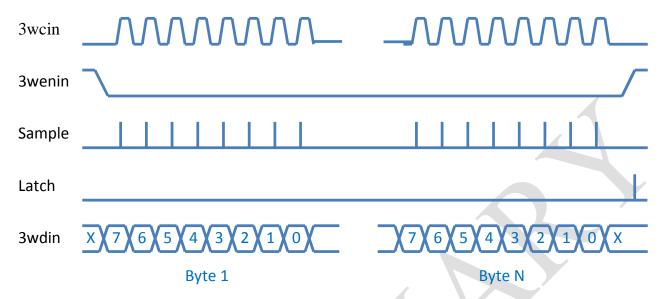

The bytes are delivered starting from 1 to 40 and bits within a byte are delivered starting from MSB. Bit#7 is the MSB of a byte as shown in Fig. 2. Internal registers are updated at a rising edge of 3wenin.

Fig. 2. SPI Operation

## POWER SUPPLY CONFIGURATION

The IC requires three positive external power supplies. The first supply v2p9 is used for the data output terminations and to power all high-speed circuitry and reference sources. The second supply v4p0 powers the internal analog adder circuitry. The digital supply v1p2 is used for the internal CMOS circuits of the SPI.

All supplies are positive in relation to the internal common node vee=0.0V.

#### ABSOLUTE MAXIMUM RATINGS

Caution: Exceeding the absolute maximum ratings may cause damage to this product and/or lead to reduced reliability. Functional performance is specified over the recommended operating conditions for power supply and temperature only. AC and DC device characteristics at or beyond the absolute maximum ratings are not assumed or implied. All min and max voltage limits are referenced to ground.

| Parameter                   | Min | Max  | Units |

|-----------------------------|-----|------|-------|

| Supply Voltage (v4p0)       |     | +4.4 | V     |

| Supply Voltage (v2p9, v2p7) |     | +3.6 | V     |

| Supply Voltage (v1p2)       |     | +1.5 | V     |

| RF Input Voltage Swing (SE) |     | 0.5  | V     |

| Case Temperature            |     | +90  | °C    |

| Storage Temperature         | -40 | +100 | °C    |

| Operational Humidity        | 10  | 98   | %     |

| Storage Humidity            | 10  | 98   | %     |

Table 4. Absolute Maximum Ratings

## **TERMINAL FUNCTIONS**

| TERMINAL                                          |                         | ERMINAL          | Dogarintian                                                          |  |  |  |

|---------------------------------------------------|-------------------------|------------------|----------------------------------------------------------------------|--|--|--|

| Name No. Type                                     |                         | Type             | Description                                                          |  |  |  |

|                                                   | High-Speed I/Os         |                  |                                                                      |  |  |  |

| d1p                                               | 51                      | CML-type input   | Differential high-speed data inputs with internal SE 500hm           |  |  |  |

| d1n                                               | 53                      |                  | terminations to v2p9                                                 |  |  |  |

| d2p                                               | 30                      | CML-type input   |                                                                      |  |  |  |

| d2n                                               | 28                      |                  |                                                                      |  |  |  |

| q1p                                               | 14                      | CML-type output  | Differential high-speed data outputs with internal SE 50 <i>Ohm</i>  |  |  |  |

| q1n                                               | 12                      |                  | terminations to v2p9; require external SE 50 <i>Ohm</i> terminations |  |  |  |

| q2p                                               | 35                      | CML-type output  | to v2p9.                                                             |  |  |  |

| q2n                                               | 37                      |                  |                                                                      |  |  |  |

|                                                   | Low-Speed I/Os          |                  |                                                                      |  |  |  |

| 3wenin                                            | 26                      | 1.2V CMOS input  | Enable input signal SSn for 3-wire interface                         |  |  |  |

| 3wcin                                             | 25                      |                  | Clock input signal SCLK for 3-wire interface                         |  |  |  |

| 3wdin                                             | 24                      |                  | Data input signal MOSI for 3-wire interface                          |  |  |  |

| 3wdout                                            | 23                      | 1.2V CMOS output | Data output signal MISO for 3-wire interface                         |  |  |  |

|                                                   | Analog Control Voltages |                  |                                                                      |  |  |  |

| v2p7                                              | 9                       | Internal voltage | Internal voltage source of v2p9-0.2V                                 |  |  |  |

|                                                   |                         | generator output |                                                                      |  |  |  |

| Analog Control Nodes (for DMM measurements only!) |                         |                  |                                                                      |  |  |  |

| qrepp                                             | 60                      | Analog DC output | Replica differential data outputs                                    |  |  |  |

| qrepn                                             | 5                       |                  |                                                                      |  |  |  |

| Supply And Termination Voltages |                       |                                                  |  |  |  |

|---------------------------------|-----------------------|--------------------------------------------------|--|--|--|

| Name                            | Description           | Pin Number                                       |  |  |  |

| vee                             | External ground       | 2, 4, 6, 11, 13, 15, 18, 20, 22, 27, 29, 31, 34, |  |  |  |

|                                 |                       | 36, 38, 43, 45, 47, 50, 52, 54, 59, 61, 63       |  |  |  |

| v2p9                            | Positive power supply | 3, 7, 10, 17, 32, 33, 44, 48, 49, 62, 64         |  |  |  |

| v4p0                            | Positive power supply | 19, 39, 40, 41, 42, 46                           |  |  |  |

| v1p2                            | Positive power supply | 1, 16                                            |  |  |  |

| nc                              | not connected pins    | 8, 21, 55, 56, 57, 58                            |  |  |  |

Office: (310) 530-9400 Fax: (310) 530-9402

www.adsantec.com

## **ELECTRICAL CHARACTERISTICS**

| PARAMETER                                 | MIN  | TYP      | MAX       | UNIT        | COMMENTS                                |  |

|-------------------------------------------|------|----------|-----------|-------------|-----------------------------------------|--|

| General Parameters                        |      |          |           |             |                                         |  |

| v2p9                                      |      | 2.9      |           | V           | Analog supply                           |  |

| v4p0                                      |      | 4.0      |           | V           | Analog supply                           |  |

| vdd                                       |      | 1.2      |           | V           | CMOS digital supply                     |  |

| vee                                       |      | 0.0      |           | V           | External ground                         |  |

| Iv2p9                                     |      | 400      |           | mА          | All taps enabled, maximum peaking       |  |

| TV2p9                                     |      | 175      |           | mА          | 3 equivalent taps in each channel       |  |

| Iv4p0                                     |      | 180      | 215       | mA          | Depending on bandwidth control settings |  |

| Power consumption                         |      | 1.25     | 2.1       | W           |                                         |  |

| Junction temperature                      | -25  | 50       | 125       | $^{\circ}C$ |                                         |  |

|                                           |      |          | FIR Para  | meters      |                                         |  |

| No. of Taps                               |      | 2x2x9    |           |             |                                         |  |

| Delay between Taps                        |      | 13.5     |           | ps          |                                         |  |

| Voltage gain                              |      | 6        |           | dB          | From chip input to chip output          |  |

|                                           | High | Speed I  | nput Data | (d1p/d1     | n, d2p/d2n)                             |  |

| Data Rate                                 | DC   |          | 28        | Gb/s        |                                         |  |

| Swing in linear mode                      |      | 110      |           | mV          | Differential or SE, p-p                 |  |

| S11                                       |      | TBD      |           | dB          |                                         |  |

| CM Voltage Level                          |      | v2p7-0.2 |           | V           | Must match for both inputs              |  |

| Analog Output Data (q1p/q1n, q2p/q2n)     |      |          |           |             |                                         |  |

| Bandwidth                                 | DC   |          | 20        | GHz         |                                         |  |

| Swing                                     |      | 220      |           | mV          | At each SE output                       |  |

| S22                                       |      | TBD      |           | dB          |                                         |  |

| CM Voltage Level                          |      | 2.5      |           | V           |                                         |  |

| DC Control Voltages                       |      |          |           |             |                                         |  |

| qrp-qrn $220$ $mV$ With optimal ch1_gnmx1 |      |          |           |             | 1 — 5                                   |  |

| 3-Wire Interface Ports                    |      |          |           |             |                                         |  |

| Clock frequency                           |      |          | 6         | MHz         |                                         |  |

| Low logic level                           |      | 0        |           | V           |                                         |  |

| High logic level                          |      | 1.2      |           | V           |                                         |  |

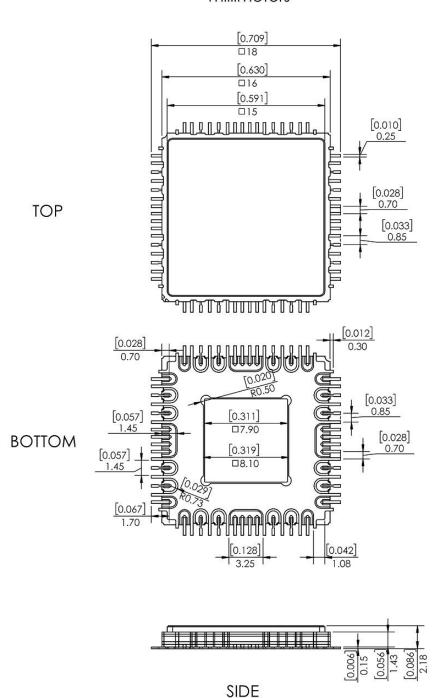

## PACKAGE INFORMATION

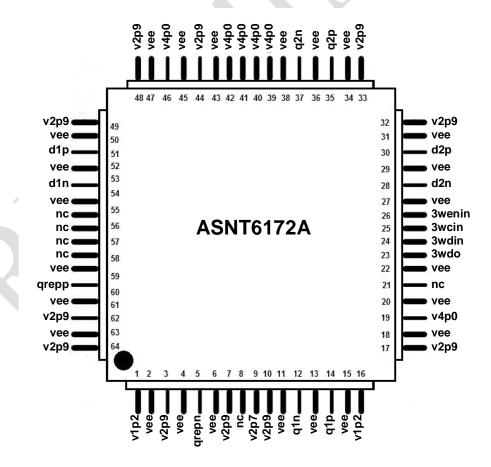

The chip die is housed in a custom, 64-pin CQFP package shown in Fig. 3. The package provides a center heat slug located on its back side to be used for heat dissipation. ADSANTEC recommends for this section to be soldered to the **vee** plain, which is ground for a positive supply.

Office: (310) 530-9400 Fax: (310) 530-9402

www.adsantec.com

# 64-PIN KMO Package

[inches] millimeters

The part's identification label is ASNT6172A-KMO. The first 9 characters of the name before the dash identify the bare die including general circuit family, fabrication technology, specific circuit type, and part version while the 3 digits after the underscore represent the package's manufacturer, type, and pin out count.

This device complies with Commission Delegated Directive (EU) 2015/863 of 4 June 2015 amending Annex II to Directive 2011/65/EU of the European Parliament and of the Council as regards the list of restricted substances (Text with EEA relevance) on the restriction of the use of certain hazardous substances in electrical and electronics equipment (RoHS Directive) in accordance with the definitions set forth in the directives for all ten substances.

### **REVISION HISTORY**

| Revision | Date    | Changes                            |

|----------|---------|------------------------------------|

| 0.2.2    | 12-2020 | Corrected pin out drawing          |

|          |         | Corrected Terminal Functions table |

|          |         | Corrected SPI byte table           |

|          |         | Updated package information        |

| 0.1.2    | 01-2020 | Updated Package Information        |

| 0.0.1    | 08-2019 | Preliminary release                |