Ultra High-Speed Mixed Signal ASICs

Office: (310) 530-9400 Fax: (310) 530-9402 www.adsantec.com

#### ASNT8110A-PQB DC-to-24*GHz* Programmable Integer Divider with SPI

- Wide frequency range from DC to 24GHz

- Continuous division ratios from 1 to 256

- 50% duty cycle of the output divided clock signal

- Fully differential CML input and output interfaces

- Adjustable power consumption

- Easy 8-bit parallel programming interface compatible with CMOS/LVTTL standards

- Optional external reset function

- Dynamic division ratio adjustment with a short set-up time (about 20*ns* after the pulse edge on any control input)

- Single +2.8*V* or -2.8*V* power supply

- Industrial temperature range

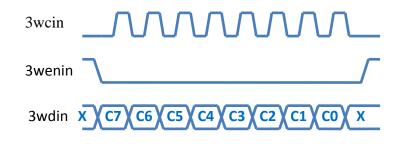

- Standard 40-pin QFN package with a thermal pad

Office: (310) 530-9400 Fax: (310) 530-9402 www.adsantec.com

# DESCRIPTION

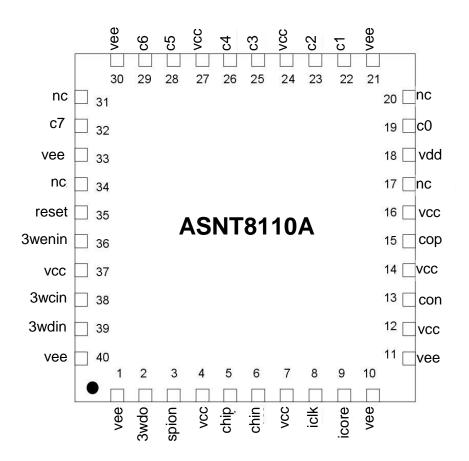

ASNT8110A-PQB is a high-speed programmable integer clock divider with dynamic adjustment of the division ratio. An optional external active-high CMOS/LVTTL reset signal is also provided. The functional block diagram of the device is shown in Fig. 1.

Fig. 1. Functional Block Diagram

The divider accepts an input clock signal (chip/chin) with a speed from DC to the maximum specified frequency and provides a clean 50% duty cycle output divided clock signal (cop/con) in any operational mode. The divider allows for dynamic adjustment of the division ratio from 1 to 256 with a step of 1 through either full-scale CMOS 8-bit parallel interface or 1.2V CMOS 3-wire SPI. The parallel or serial interface mode is selected with a full-scale CMOS control signal spion.

In the parallel mode, a binary code on the control inputs (c0-c7) defines the value of the ratio from 1 to 255, where c7 is the most significant bit (MSB). All "0"s ("low" state) define the division by 256. Following any change of any control signal, the divider switches to idle after (64...128) periods of the high-speed system clock plus an additional 1.6*ns* delay, and returns back to normal operation with the new division ratio after an additional delay equal to 192 periods of the high-speed system clock.

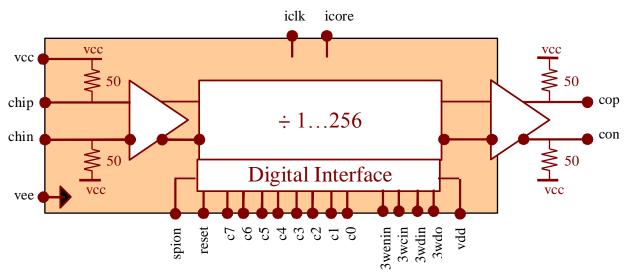

In the serial mode, the 1-byte division coefficient code is supplied through the 3-wire interface with MSB first as shown in Fig. 2. Input data **3wdin** are sampled at rising edges of SPI clock **3wcin** and internal division coefficient value will be updated at a rising edge of the **3wenin** signal.

Fig. 2. SPI Bit Order

Office: (310) 530-9400 Fax: (310) 530-9402 www.adsantec.com

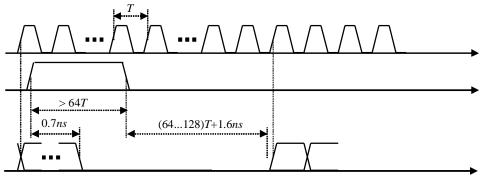

The device automatically resets itself after the initial power-up and any change of the division control signals. When the optional external reset signal **reset** is set to "high", the divider switches to idle (static "0" output) after a 0.7*ns* delay as shown in the timing diagram in Fig. 3. When **reset** returns to "low", the divider switches back to normal operation after (64...128) periods of the high-speed system clock plus an additional 1.6*ns* of delay. The minimum allowed **reset** pulse must be longer than 64 periods of the high-speed system clock.

Fig. 3. Timing Diagram

The part's I/O's support the CML logic interface with on chip 50*Ohm* termination to **vcc** and may be used differentially, AC/DC coupled, single-ended, or in any combination (also see POWER SUPPLY CONFIGURATION). In the DC-coupling mode, the input signal's common mode voltage should comply with the specifications shown in ELECTRICAL CHARACTERISTICS. In the AC-coupling mode, the input termination provides the required common mode voltage automatically. The differential DC signaling mode is recommended for optimal performance.

# POWER SUPPLY CONFIGURATION

The part can operate with either a negative supply (vcc=0.0V=ground), or a positive supply (vee = 0.0V = ground). In case of the positive supply, all I/Os need AC termination when connected to any devices with 50*Ohm* termination to ground. Different PCB layouts will be needed for each different power supply combination.

The parts power consumption may be reduce by up to 30% using external resistors to connect the control ports iclk and icore to vee. It is recommended to activate iclk first and then activate icore if required because current reduction results in a lower maximum operational frequency and icore has larger impact than iclk!

#### All the characteristics detailed below assume vcc = +2.8V and vee = 0V.

# **ABSOLUTE MAXIMUM RATINGS**

Caution: Exceeding the absolute maximum ratings shown in Table 1 may cause damage to this product and/or lead to reduced reliability. Functional performance is specified over the recommended operating conditions for power supply and temperature only. AC and DC device characteristics at or beyond the absolute maximum ratings are not assumed or implied. All min and max voltage limits are referenced to ground.

Ultra High-Speed Mixed Signal ASICs

Office: (310) 530-9400 Fax: (310) 530-9402 www.adsantec.com

| Parameter                   | Min | Max  | Units |

|-----------------------------|-----|------|-------|

| Supply Voltage (VCC)        |     | +3.3 | V     |

| Power Consumption           |     | 3.2  | W     |

| RF Input Voltage Swing (SE) |     | 1.0  | V     |

| Case Temperature            |     | +90  | °С    |

| Storage Temperature         | -40 | +100 | °С    |

| Operational Humidity        | 10  | 98   | %     |

| Storage Humidity            | 10  | 98   | %     |

# **TERMINAL FUNCTIONS**

| TERMINAL |                 | IINAL                 | DESCRIPTION                                                                  |  |  |  |

|----------|-----------------|-----------------------|------------------------------------------------------------------------------|--|--|--|

| Name     |                 |                       |                                                                              |  |  |  |

|          | High-Speed I/Os |                       |                                                                              |  |  |  |

| chip     | 5               | CML input             | Differential clock inputs with internal SE 50 <i>Ohm</i> termination to VCC. |  |  |  |

| chin     | 6               |                       |                                                                              |  |  |  |

| cop      | 15              | CML output            | Differential divided clock outputs with internal SE 500hm                    |  |  |  |

| con      | 13              |                       | termination to vcc. Require external SE 500hm termination to vcc.            |  |  |  |

|          |                 |                       | Low-Speed I/Os                                                               |  |  |  |

| reset    | 35              | vee/vcc<br>CMOS input | External active-high reset port                                              |  |  |  |

| 3wenin   | 36              | 1.2V CMOS             | 3-wire enable active-low signal (SSn)                                        |  |  |  |

| 3wcin    | 38              | input                 | 3-wire input clock (SCLK)                                                    |  |  |  |

| 3wdin    | 39              | -                     | 3-wire input data (MOSI)                                                     |  |  |  |

| 3wdo     | 2               | 1.2V CMOS             | 3-wire ouptut data (MISO)                                                    |  |  |  |

|          |                 | output                |                                                                              |  |  |  |

|          |                 |                       | Digital Controls                                                             |  |  |  |

| spion    | 3               | vee/vcc               | External SPI activation port (active: high, SPI is enabled; default: low,    |  |  |  |

|          |                 | CMOS input            |                                                                              |  |  |  |

| c0       | 19              | vee/vcc               | Division binary control signals                                              |  |  |  |

| c1       | 22              | CMOS input            |                                                                              |  |  |  |

| c2       | 23              |                       |                                                                              |  |  |  |

| c3       | 25              |                       |                                                                              |  |  |  |

| c4       | 26              |                       |                                                                              |  |  |  |

| c5       | 28              |                       |                                                                              |  |  |  |

| c6       | 29              |                       |                                                                              |  |  |  |

| c7       | 32              |                       |                                                                              |  |  |  |

|          |                 |                       | Analog Controls                                                              |  |  |  |

| iclk     | 8               | Analog input          | Power control ports with internal 800 <i>Ohm</i> termination to vee; require |  |  |  |

| icore    | 9               |                       | external resistors between 1200hm and 6K0hm connected to vee or              |  |  |  |

|          |                 |                       | external power supplies with current sinking capability; may be left         |  |  |  |

|          |                 |                       | not connected                                                                |  |  |  |

Ultra High-Speed Mixed Signal ASICs

Office: (310) 530-9400 Fax: (310) 530-9402 www.adsantec.com

| Supply And Termination Voltages |                                      |                              |  |

|---------------------------------|--------------------------------------|------------------------------|--|

| Name                            | Description                          | Pin Number                   |  |

| vcc                             | Main positive power supply or ground | 4, 7, 12, 14, 16, 24, 27, 37 |  |

| vdd                             | Digital positive power supply        | 18                           |  |

| vee                             | Negative power supply or ground      | 1, 10-11, 21, 30, 33, 40     |  |

| nc                              | Not connected pins                   | 17, 20, 31, 34               |  |

#### **ELECTRICAL CHARACTERISTICS**

| PARAMETER              | MIN                            | TYP     | MAX                  | UNIT       | COMMENTS                                    |

|------------------------|--------------------------------|---------|----------------------|------------|---------------------------------------------|

| General Parameters     |                                |         |                      |            |                                             |

| vee                    | 0.0 V External ground          |         | External ground      |            |                                             |

| VCC                    | 2.6                            | 2.8     | 3.0                  | V          |                                             |

| vdd                    | 1.2                            |         | 1.3                  | V          | very low current consumption                |

| Ivee                   |                                | 920     |                      | mA         | R=120 <i>Ohm</i> between iclk/icore and vee |

|                        |                                | 1250    |                      | mA         | R>6KOhm between iclk/icore and vee          |

| Power consumption      |                                | 2.6     |                      | W          | R=120 <i>Ohm</i> between iclk/icore and vee |

|                        |                                | 3.5     |                      | W          | R>6KOhm between iclk/icore and vee          |

| Junction temperature   | -25                            | 50      | 125                  | °C         |                                             |

| Input (chip/chin)      |                                |         |                      |            |                                             |

| Frequency              | 0.0                            |         | 24                   | GHz        |                                             |

| Swing                  | 75                             | 400     | 1000                 | mV         | Differential or SE, p-p; at 6GHz            |

| CM Level               | vcc- (SE swing)/2              |         |                      |            |                                             |

| <b>Rise/Fall Times</b> |                                |         | 3                    | ns         | 20%-80%                                     |

|                        |                                |         | Outpu                | it (cop/co | n)                                          |

| Frequency              | 0.0                            |         | 24                   | GHz        |                                             |

| Logic "1" level        |                                | VCC     |                      | V          |                                             |

| Logic "0" level        |                                | vcc-0.6 | 5                    | V          | With external 500hm DC termination          |

| Rise/Fall Times        | 15                             | 17      | 19                   | ps         | 20%-80%                                     |

| Additive Jitter        |                                | TBD     |                      | ps         | Peak-to-Peak                                |

| Duty Cycle             | 47%                            | 50%     | 53%                  |            | For clock signal                            |

|                        | Select (c0-c7) & Reset (reset) |         |                      |            |                                             |

| Logic "1" level        | Vc                             | c-0.4   |                      | V          |                                             |

| Logic "0" level        |                                | V       | v <sub>EE</sub> +0.4 | V          |                                             |

# PACKAGE INFORMATION

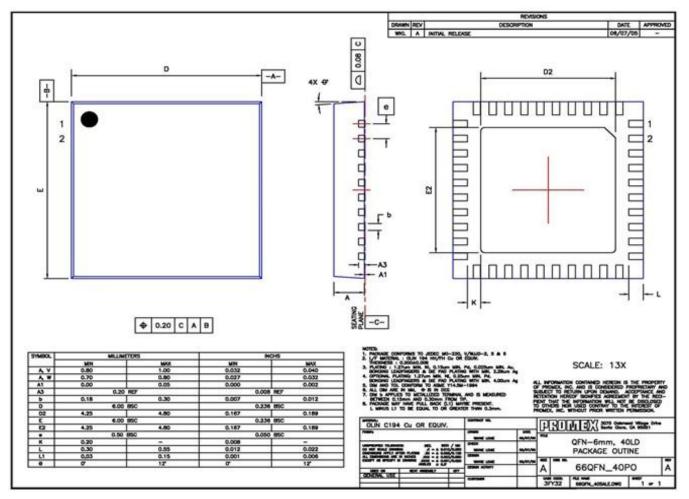

The chip is packaged in a standard 40-pin QFN package shown Fig. 4. It is recommended that the center heat slug located on the back side of the package is soldered to ground to help dissipate heat generated by the chip during operation.

The part's identification label is ASNT8110A-PQB. The first 9 characters of the name before the dash identify the bare die including general circuit family, fabrication technology, specific circuit type, and part version while the 3 characters after the dash represent the package's manufacturer, type, and pin out count.

Office: (310) 530-9400 Fax: (310) 530-9402 www.adsantec.com

This device complies with the Restriction of Hazardous Substances (RoHS) per 2011/65/EU for all ten substances.

Fig. 4. QFN 40-Pin Package Drawing (All Dimensions in mm)

# **REVISION HISTORY**

| Revision | Date    | Changes                                            |  |  |

|----------|---------|----------------------------------------------------|--|--|

| 1.3.2    | 02-2020 | Updated Package Information                        |  |  |

| 1.2.2    | 10-2019 | Corrected input swing specifications               |  |  |

| 1.1.2    | 08-2019 | Corrected header                                   |  |  |

|          |         | Corrected termination conditions for control ports |  |  |

|          |         | Corrected minimum current/power consumption        |  |  |

| 1.0.1    | 07-2017 | Corrected title                                    |  |  |

|          |         | Corrected maximum speed                            |  |  |

|          |         | Corrected power consumption                        |  |  |

|          |         | Corrected package drawing                          |  |  |

| 0.0.1    | 04-2017 | Preliminary release                                |  |  |