Product Details

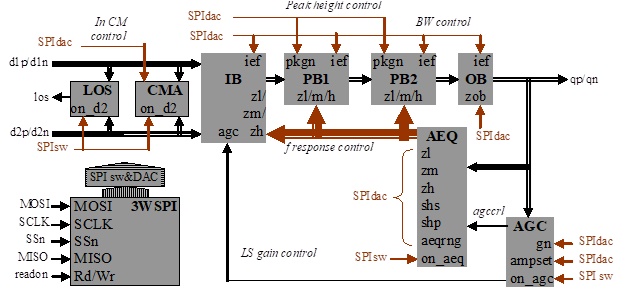

Fig. 1 Functional Block Diagram

The ASNT6751 is an adjustable continuous-time linear equalizer (CTLE) with a possibility of manual or automatic adaptation to a user-defined frequency response. All manual adjustments are achieved through a 3-wire SPI. One of two input signals d1p/d1n or d2p/d2n, selected by the on_d2 SPI bit, passes through an equalization data path that consists of four linear current-switching stages. The AC response of the data path can have a variable peak within a certain frequency range. In manual mode (SPI bits on_agc and on_aeq are set to “0”), the channel’s gain can be adjusted by the SPI bytes pkgn (Pk in datasheet) and gn (gain in datasheet). The peak’s value, position, and shape can be adjusted by SPI bytes zl (Lz in datasheet), zm (Mz in datasheet), zh (Hz in datasheet), zob (Obz in datasheet), pkgn (Pk in datasheet), and ief (BW in datasheet). Before activation of the automatic adaptation mode, the channel needs an initial calibration for the worst input signal conditions using manual controls zob, pkgn, and ief, while the SPI bits on_agc and on_aeq are set to “0”. The controls zl, zm, and zh should be set to maximum codes respectively. After activation of the automatic adaptation mode (SPI bytes on_agc and on_aeq are set to “1”), the part automatically adjusts to an user-defined output amplitude set by the SPI byte ampset and to an optimal frequency response that corresponds to the best possible eye opening of the output signal. During adaptation, the low-frequency, medium-frequency, and high-frequency zeros are gradually activated one-by-one with a certain overlap that can be controlled by the SPI byte aeqrng.

The part’s I/Os support CML-type differential interface with on-chip 50Ohms termination to vcc. Matching external terminations are also required. Critical internal voltages can be controlled through DC test points (agccrl, ampcrl, fwrhcrl, fwrlcrl) that need capacitive decoupling to vee on PCBs. All operational modes of the chip are controlled through a high-speed 3-wire serial interface (3wSPI). The SPI can operate in a normal write-read mode when its internal registers are updated with every writing cycle, or in a pure reading mode when it outputs the contents of its registers without updating them. Switching between the reading mode and the writing mode of the SPI is performed by the active-low external binary signal rdon. The SPI supply voltage can be controlled or adjusted through pin v1p2. The part operates with a positive supply vcc = +3.3V for the main data path, and additional positive supplies v4p3 = +4.3V for the AC control circuitry and v3p7 = +3.7V for the input buffer stage. The negative supply rail vee should be connected to external ground.