Product Details

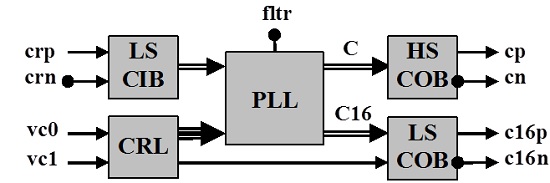

Fig. 1 Functional Block Diagram

ASNT8151-KHC is a clock multiplication unit (CMU) with a triple-range phase-locked loop (PLL) incorporating three high-speed voltage-controlled oscillators: VCO1 (lower frequency), VCO2 (medium frequency), and VCO3 (higher frequency). The chip shown in Fig. 1 generates a high-speed clock signal cp/cn with its phase and frequency locked to those of the incoming reference clock crp/crn. The differential clock cp/cn with frequency f is delivered to the output by CML output buffer HS COB. The reference clock crp/crn with frequency f/16 is accepted by LVDS input buffer LS CIB. The chip also generates a divided-by-16 clock signal c16p/c16n with frequency f/16 that is delivered to the output by LVDS output buffer LS COB. One of the VCOs is activated using two 3-state control signals vc0 and vc1. The same control signals are used to activate or disable the output buffer LS COB. When operating in closed-loop mode, the PLL requires an external loop filter connected to pin fltr. The PLL also supports an open-loop mode of operation with its selected VCO controlled externally by a voltage applied to the filter pin fltr.

The part’s high-speed output buffer supports the CML logic interface with on chip 50Ω termination to vcc and may be used differentially, AC/DC coupled, single-ended, or in any combination. The part’s low-speed I/Os support the LVDS interface with internal 100Ω termination between the direct and inverted lines. The differential DC signaling mode is recommended for optimal performance.