Product Details

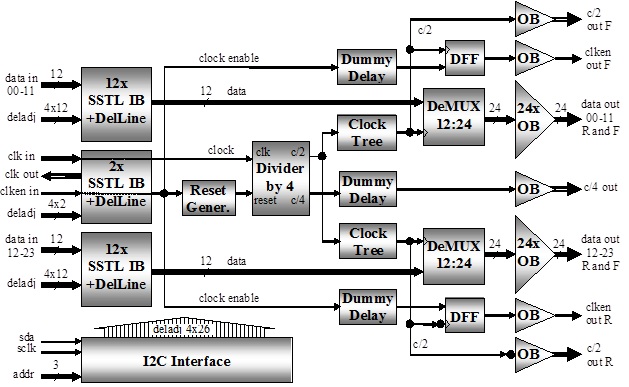

Fig. 1. Functional Block Diagram

This part is now obsolete.

ASNT2031-MBL is a broad-band 1.0Mbps-to-2.0Gbps multi-channel digital deserializer-demultiplexer (DMUX) 24-to-48 with external initial preset functionality and 1.5V single-ended SSTL1.5 input and output interfaces for data and preset signals, as well as matching differential interfaces for clock signals.

The part includes active variable delay lines (DelLine) in each input data and clock path for accurate signal alignment at the DMUX register inputs in order to define the optimal sampling point for the input data signals (“data in”). The value of each delay is externally controlled through an I2C interface with a user-selectable 3-bit chip address.

The operational speed of DMUX is defined by an external clock signal (“clk in”) that is converted into the required timing signals by an internal divider and is also supplied to the output of the chip (“clk out”). The divider can be preset to a certain initial state by the external clock enable signal (“clken in”), which allows synchronization of multiple DMUX devices operating in parallel.