Product Details

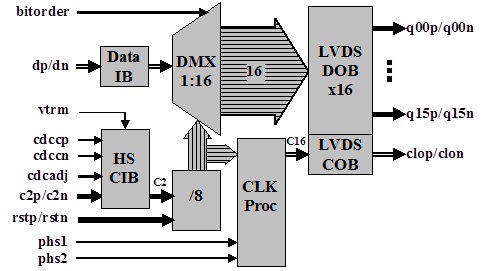

Fig. 1 Functional Block Diagram

ASNT2140 is a high-speed DDR (dual data rate) digital 1-to-16 demultiplexer (DMX) / deserializer. The IC shown in Fig. 1 functions seamlessly over the specified range of data rates (fbit). The main function of the IC is to demultiplex a high-speed serial bit stream running at fbit into 16 parallel data channels running at a bit rate of fbit/16. It accepts a high-speed data transmitted over a controlled impedance media of 50Ohm. The transmission media can be a printed circuit board or copper coaxial cables. The functional distance of the data transfer is dependent upon the attenuation characteristics of the transportation media and the degree of noise coupling to the signaling environment.

During normal operation, the deserializer’s CML data input buffer (Data IB) accepts a HS serial input data signal dp/dn and delivers it to the demultiplexer’s core (DMX1:16) for deserialization. A half-rate CML sampling clock (a full-rate clock divided by 2) must be provided by an external source to the inputs c2p/c2n of the high-speed clock input buffer (HS CIB) where it is routed to the internal divider-by-8 (/8). The high-speed CML data and clock input buffers provide on-chip 50Ohm termination and are designed to be driven by devices with 50Ohm source impedance. The duty cycle of the internal clock c2 can be adjusted either through a single ended control pin cdcadj or through a dual control port cdccp/cdccn. The clock input buffer uses a separate positive supply vtrm for additional common mode voltage adjustment. The divider provides signaling for DMX1:16 and produces a divided-by-16 full-rate forwarded clock C16 for the low-speed LVDS-compliant clock output buffer (LVDS COB). The divider can be preset to a certain initial state using external CML signals rstp/rstn. The phase of the low-speed forwarded clock clop/clon can be modified in 90° increments by utilizing pins phs1 and phs2 and the clock processing block (CLK Proc).

The deserialized digital words are delivered to the output parallel interface through 16 LVDS-compliant data output buffers LVDS DOBx16. By utilizing the pin bitorder, the deserializer can designate either q00p/q00n or q15p/q15n as the MSB (most significant bit that is delivered first to the serial interface), thus simplifying the interface between the demultiplexer and a following ASIC. The chip uses a single +3.3V power supply and is characterized for junction temperature from −25°C to 125°C of junction temperature.