Product Details

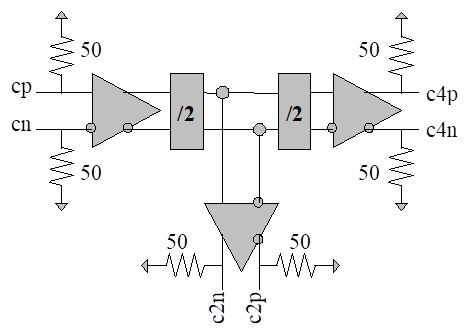

Fig.1 Functional Block Diagram

ASNT8130-KMC is a high-speed, low-power divider by-2 and by-4. The part shown in Fig. 1 accepts a CML input clock signal (cp/cn) with the speed from DC to maximum operational frequency and provides clean 50% duty cycle output signals with divided-by-2 (c2p/c2n) and divided-by-4 (c4p/c4n) frequency. The part’s I/Os support the CML logic interface with on chip 50Ω termination to vcc and may be used differentially, AC/DC coupled, single-ended, or in any combination. The part can operate with either negative supply (vcc = 0.0V =ground and vee = -3.3V), or positive supply (vcc = +3.3V and vee = 0.0V = ground). In case of the positive supply, all I/Os need AC termination when connected to any devices with 50Ω termination to ground. Different PCB layouts will be needed for each different power supply combination.